Unlock NeuralNation Transform On-Demand

All in-person passes for NeuralNation Transform 2024 are sold out! Secure your spot now for exclusive on-demand access post-conference. Learn More

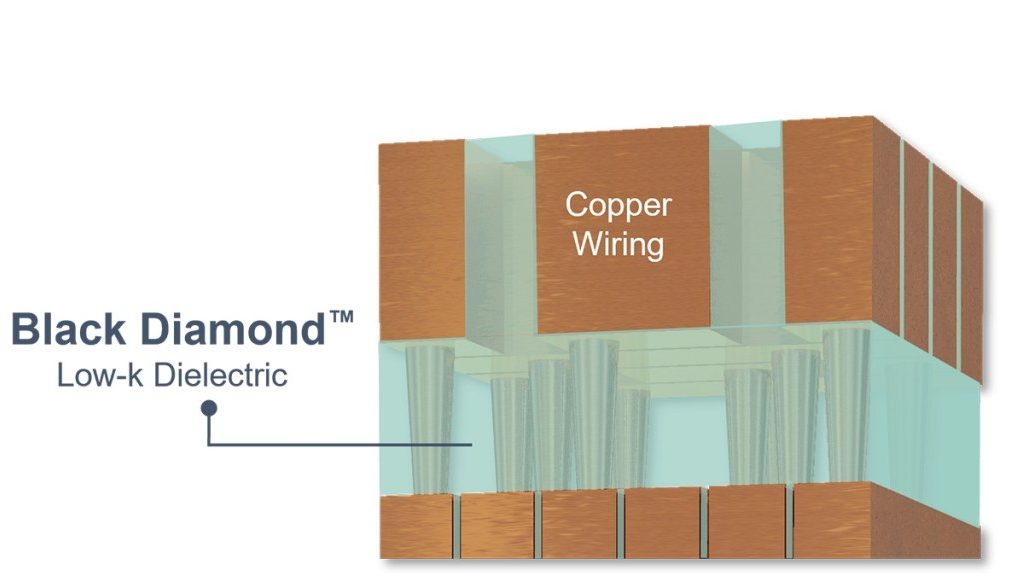

He mentioned that the advanced Black Diamond technology is now being embraced by all major logic and memory chip manufacturers.

“One of our main challenges in the low-k material realm for this matrix is to overcome the trade-off between dielectric constant and mechanical strength,” Bhatnagar explained. “Customers are eager to reduce the dielectric constant to minimize capacitance and signal noise between lines.”

“There’s always been a trade-off between lowering the dielectric constant and increasing the mechanical strength of the dielectric. Our new material, engineered at the molecular level, has successfully broken this trade-off barrier. Through molecular engineering in this matrix, we have developed a new low-k material that eliminates this trade-off,” he added.

“Our goal is to reduce capacitance by lowering the dielectric constant. Capacitance is directly linked to this constant. By reducing it and simultaneously enhancing mechanical strength, we are breaking new ground,” Bhatnagar emphasized. “Usually, there’s a trade-off involved. However, with the introduction of this new molecule into the enhanced Black Diamond, we have managed to break this trade-off and shift the paradigm.”

New binary metal liner enables ultrathin copper wires

To scale chip wiring, chipmakers etch each layer of low-k film to create trenches, then deposit a barrier layer that prevents copper from migrating into the chip and creating yield issues. The barrier is then coated with a liner that ensures adhesion during the final copper reflow deposition sequence, which slowly fills the remaining volume with copper.

As chipmakers further scale the wiring, the barrier and liner take up a larger percentage of the volume intended for wiring, and it becomes physically impossible to create low-resistance, void-free copper wiring in the remaining space.

Today, Applied Materials introduced its latest IMSTM (Integrated Materials Solution) which combines six different technologies in one high-vacuum system, including an industry-first combination of materials that enables chipmakers to scale copper wiring to the 2nm node and beyond. The solution is a binary metal combination of ruthenium and cobalt (RuCo), which simultaneously reduces the thickness of the liner by 33 percent to 2nm, produces better surface properties for void-free copper reflow, and reduces electrical line resistance by up to 25% to improve chip performance and power consumption.

The focus has been to make the wiring better and improve the dielectric on the wiring. As the features shrink, it gets harder to put copper wiring into the trenches without creating what are known as voids, where there is a section that didn’t get copper into it. This impacts resistance and yield as well. Resistance keeps coming back as a problem with each generation of chips.

Now the company is switching to a combination of ruthenium and cobalt as the liner between the copper and the film. It can reduce the thickness of the liner by up to 33%. The result is there is more room for the copper in the trench, and that widens the effective wire, which lowers the resistance. Performance goes up. The width of these sections in the structure is microscopic and it results in better yields.

The new Applied Endura Copper Barrier Seed IMS with Volta Ruthenium CVD (chemical vapor deposition) is being adopted by all leading logic chipmakers and began shipping at the 3nm node. An animation can be viewed here.

Customer comments

“While advances in patterning are driving continued device scaling, critical challenges remain in other areas including interconnect wiring resistance, capacitance and reliability,” said Sunjung Kim, VP and head of the foundry development Team at Samsung Electronics, in a statement. “To help overcome these challenges, Samsung is adopting multiple materials engineering innovations that extend the benefits of scaling to the most advanced nodes.”

“The semiconductor industry must deliver dramatic improvements in energy-efficient performance to enable sustainable growth in AI computing,” said Y.J. Mii, EVP and co-COO at TSMC, in a statement. “New materials that reduce interconnect resistance will play an important role in the semiconductor industry, alongside other innovations to improve overall system performance and power.”

A growing wiring opportunity

Applied is the industry leader in chip wiring process technologies. From the 7nm node to the 3nm node,

interconnect wiring steps have approximately tripled, increasing Applied’s served available market opportunity by more than $1 billion per 100,000 wafer starts per month (100K WSPM) of greenfield capacity, to approximately $6 billion.

Looking ahead, the introduction of backside power delivery is expected to increase Applied’s wiring opportunity by another $1 billion per 100K WSPM, to approximately $7 billion.

One research initiative that Intel recently talked about focused on making wiring better through the backside of a chip, which normally isn’t used for wiring. This architectural change takes power lines from the front of the chip to the backside, where the wiring needs to be thicker. But frontside wiring needs improvements as well, and so these improvements are all happening in parallel, Jansen said.

The addition of backside wiring reduces complexity and that helps get more efficient routing and better performance and power consumption, Jansen said. But the frontside improvements are also necessary to enable scaling.

About 20 years ago, the wiring moved away from aluminum to dielectrics and copper. To drive more performance every year, the industry has been adding more materials to create stronger wires that are more energy efficiency. The chip equipment etches trenches and vias into the film on the chip surfaces, and then ultimately fills those gaps with copper for wiring. Copper is the main way to conduct electrons through the chip. Now the materials serve as a barrier between the copper and the dielectric so they don’t contaminate each other.

“Without materials innovation, the barriers and the liners are starting to occupy more and more of that trench volume. So this scaling creates a couple of different challenges. As copper wires shrink, resistance goes up. This is sort of a basic physics (fact). Thinner wires are going to create higher resistance. There isn’t really a good way around that,” Jansen said.

He added, “And so what we’re trying to do is improve the amount of that wire that is dedicated to convert. Secondly, as these things shrink, the wires are getting closer and closer together. And so there’s less space for the dielectric that is surrounding them. And as a result, you have electrical crosstalk. You can get signal delays, distortion, and altogether this cost in performance and power consumption. So that’s the opposite of what we’re trying to do.”

To make enhancements for demanding AI chips, the performance and efficiency has to keep getting better.

The new chip wiring products, along with other materials engineering innovations for making future AI chips, will be discussed at Applied’s Semicon West 2024 Technology Breakfast.

Better GPUs and AI chips

All of this work is aimed at making better GPUs and other AI chips that can handle rnrnThe future demands are clear, according to Applied Materials spokesmen. They believe that these wiring advancements are crucial for the chip industry to continue its trend of three times improvement every two years in energy efficiency.

“This is a game-changing technology for 2nm and beyond,” Jansen emphasized.

Bhatnagar highlighted the importance of stacking memory chips to fuel AI processors, emphasizing the need for high mechanical strength for 3D stacking capability. This technology allows chips to achieve high computing performance without overheating.

“One of the main drivers for these materials is the high-bandwidth memory requirements for AI,” Bhatnagar explained.

Jansen pointed out, “I believe that the pace at which new technologies are advancing, extending Moore’s Law and increasing transistor density per area, is in line with the research aiming to reach a trillion-transistor GPU. Nvidia’s Blackwell currently has around 208 billion transistors. AMD will also be present at Applied Materials’ event this week.